Jui-Yu Hung

ABOUT ME

Digital IC design engineer with {Loading Calculator} years of industry experience. The products include TDMA, LTE, NR modem, AI accelerator, high-speed IO(USB,HUB,DP,PCIe,Ethernet), TCP/IP protocol and HFT system. Skilled at low cost, low power and low latency design. Experienced in integration, front-end, middle-end and FPGA design flow. Capable of building design verification environment in SystemVerilog & UVM.

EDUCATIONS

National Tsing-Hua University

Taiwan

Master of Engineering in Department of Electrical Engineering

Master in EE

Jul. 2015

- Expertise field: memory integrated circuit designs

- Major in High-Speed Memory Sense Amplifier design

- Conducted Projects of SRAM, NV-TCAM, RRAM, NAND-Flash, 3D-TSV.

Bachelor of Engineering in Department of Electrical Engineering

Bechelor in EE

Jun. 2013

- Graduating in the honor of the top-rated prize

EMPLOYMENT

VICI Holdings, Taiwan

HFT Digital Design Engineer

Dec.2024-NOW

Algoltek, Taiwan

ASIC Design Engineer

Apr.2022-Dec.2024

MemryX, Taiwan

ASIC Design Engineer

Sep.2020-Apr.2022

Mediatek, Taiwan

ASIC Design Engineer

Nov.2015-Sep.2020

SKILLS

- Programming language:

Verilog-2005, SystemVerilog, Tcl, C/C++, Perl, Lua, Rust, Javascript, Typescript, SQL - Tools:

VCS, Xrun, Verdi, Simvision, DC, Genus, VC Formal, LEC, STA, SG-lint, SG-cdc, PTPX, Power-Artist, Vivado - Frameworks:

UVM

PATENTS AND PUBLICATIONS

Published Papers:

- “A 256b-wordlength ReRAM-based TCAM with 1ns search-time and 14x improvement in wordlength-energyefficiency-density product using 2.5T1R cell ”IEEE International Solid-State Circuits Conference (ISSCC), Feb 2016.

- “Alow-powersubthreshold-to-superthresholdlevel-shifterforsub-0.5VembeddedresistiveRAM (ReRAM) macro in ultra low-voltage chips”IEEE Asia Pacific Conference on Circuit and Systems(APCCAS), Nov. 2014.

Patents:

- “Sense Amplifier”, United States Patent US 9378780 B1 Active Jun., 2015

SIDE PROJECTS

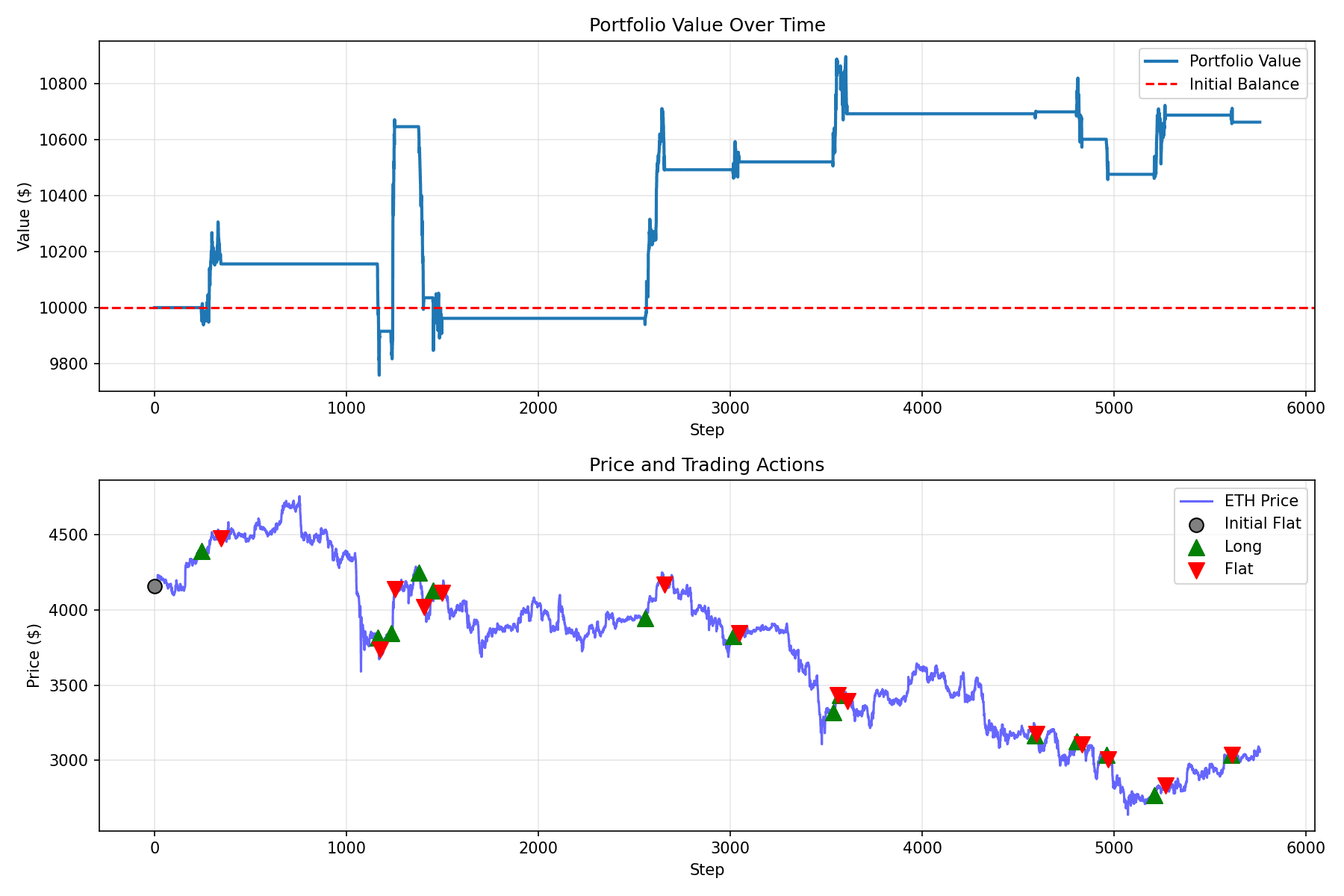

Crypto AI Trading System:

- Language: Python, Typescript

- Description: AI-powered cryptocurrency trading system with automated strategy execution and real-time market analysis. Using Pytorch to train model and do backtesting. Using Node.js to do live trading.

- Features: Reinforcement Learning, Backtesting, ONNX

- Project Status: Active

- Interim results: